February 1980

# Implementation of a Scanning Spectrum Analyzer Using the 2920 Signal Processor

Robert E. Holm

John S. Rittenhouse

Telecommunications

Product Marketing

**FABIO MONTORO**

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use, duplication or disclosure is subject to restrictions stated in Intel's software license, or as defined in ASPR 7-104.9 (a) (9). Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Intel Corporation.

The following are trademarks of Intel Corporation and may only be used to identify Intel products:

|        |                 |             |

|--------|-----------------|-------------|

| BXP    | Intelelevision  | MULTIBUS    |

| i      | Intellec        | Multimodule |

| ICE    | iSBC            | PROMPT      |

| ICS    | iSBX            | Promware    |

| i'm    | Library Manager | RMX         |

| Insite | MCS             | UPI         |

| Intel  | Megachassis     | µScope      |

|        | Micromap        |             |

and the combinations of ICE, iCS, iSBC, MCS or RMX and a numerical suffix.

Additional copies of this manual or other Intel literature may be obtained from:

Literature Department

Intel Corporation

3065 Bowers Avenue

Santa Clara, CA 95051

---

# Implementation of a Scanning Spectrum Analyzer Using the 2920 Signal Processor

## Contents

---

|                                                                          |    |

|--------------------------------------------------------------------------|----|

| <b>1.0 INTRODUCTION</b> .....                                            | 1  |

| <b>2.0 SAMPLED DATA SYSTEM</b> .....                                     | 1  |

| 2.1 Block Diagram Description .....                                      | 1  |

| 2.2 Sampling Theory .....                                                | 2  |

| 2.3 Quantization Noise .....                                             | 4  |

| 2.4 Signal Reconstruction .....                                          | 4  |

| <b>3.0 2920 SIGNAL PROCESSOR DESCRIPTION</b> .....                       | 5  |

| 3.1 Analog Operations .....                                              | 5  |

| 3.2 Digital Operations .....                                             | 5  |

| 3.3 The 2920 Instruction Set .....                                       | 6  |

| <b>4.0 DESCRIPTION OF SPECTRUM ANALYZER</b> .....                        | 8  |

| 4.1 Specifications .....                                                 | 8  |

| 4.2 Block Diagram Description .....                                      | 8  |

| 4.3 Sampled Data System Considerations .....                             | 8  |

| <b>5.0 DESCRIPTION OF SUBSYSTEM IMPLEMENTATION</b> .....                 | 10 |

| 5.1 Anti-aliasing Filter .....                                           | 10 |

| 5.2 Sweep Rate Generator (SRG) and Sweeping Local Oscillator (SLO) ..... | 10 |

| 5.3 Implementation of a 4 Quadrant Multiplier .....                      | 12 |

| 5.4 Design and Implementation of the Output Lowpass Filter .....         | 13 |

| 5.5 Logarithmic Amplifier .....                                          | 15 |

| <b>6.0 SUMMARY</b> .....                                                 | 17 |

| <b>APPENDIX A. Complete Spectrum Analyzer Assembly Listing</b> .....     | 18 |

## 1.0 INTRODUCTION

The purpose of a scanning spectrum analyzer is to determine the long term spectral characteristics of an analog signal. This is done by sweeping the input signal through a bandpass filter and displaying the filter output as a function of time. This application note describes the implementation of a sampled data scanning spectrum analyzer using the 2920 Signal Processor.

A scanning spectrum analyzer embodies many of the functions which can be found in a broad class of analog applications. These functions include: lowpass and bandpass filters, multipliers (mixers), detectors, and oscillators. The spectrum analyzer is a useful circuit which lends itself to applications such as speech processing, industrial control, medical electronics, signal detection, and signal processing.

The implementation of a spectrum analyzer using a sampled data system requires an understanding of sampling theory and digital signal processing as well as the ability to specify the system in analog terms. A basic review of sampling theory is provided in Section 2. Section 3 describes the 2920 Signal Processor. Section 4 describes the block diagram of the spectrum analyzer and discusses the design considerations. Once the block diagram of the application is complete, it is relatively straightforward to implement each subsystem as a block of code in the 2920 Signal Processor. Section 5 describes the implementation of the spectrum analyzer then gives a more detailed look at the actual design process using the signal processor resulting in the final 2920 assembly language program. A complete listing of the spectrum analyzer program is given in Appendix A.

## 2.0 SAMPLED DATA SYSTEM

Sampled data systems can be implemented using either analog or digital processing techniques or both. Examples of analog processing include transversal filters using CCD or bucket brigade shift registers and analog tap weights to implement transfer characteristics. The identical characteristics can also be implemented using digital processing. Since the use of digital processors are of interest here, it is useful to investi-

gate the elements of a general purpose signal processor using a digital implementation.

### 2.1 Block Diagram Description

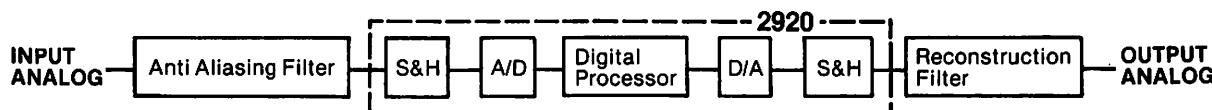

The block diagram shown in Figure 2.1 illustrates the basic blocks of a general purpose sampled data system using a digital signal processor. In this configuration it is assumed that both the input and output signals will be analog. (This is not a necessary condition since digital signals can be considered a special type of analog signal and processed accordingly.) The following paragraphs describe the function of each block in Figure 2.1.

**Anti-Aliasing Filter** — This filter is used to bandlimit the incoming analog signal prior to sampling (thus a continuous analog filter is used) so that distortion terms (aliasing noise) due to the sampling process are minimized.

**Input Sample and Hold (S&H)** — The filtered input signal is sampled at an instant in time and the resulting sampled amplitude is held long enough for subsequent processing such as analog/digital conversion (Hold time  $\leq$  the sample period).

**Input Analog to Digital Converter (ADC)** — The held analog voltage is converted to a digital word by comparing the voltage to discrete thresholds representing the digital words.

**Digital Processor** — This can be a general purpose processor or one specifically built to perform a predetermined algorithm. Typically, a general purpose microprocessor can be programmed to perform any function but the resulting execution time is too limiting for most real-time applications. A programmable digital signal processor such as the 2920 eliminates this problem because it is designed specifically for high speed signal processing while at the same time preserving its general purpose nature.

**Digital to Analog Converter (DAC)** — The processed digital words are converted back to analog using the DAC. Again, the analog signal is approximated by

**Anti Aliasing Filter:** Bandlimits input signal to reduce distortion due to sampling

**S & H:** Sample and hold performs sampling process and holds data sufficiently long for processing

**A/D:** Analog to digital conversion, generates a digital word to represent held analog voltage

**Digital Processor:** Implement transfer function using digital processing (under software control)

**D/A:** Converts digital words to analog voltages

**Reconstruction Filter:** Smooths D/A or S & H waveforms to recover continuous analog output signal

Figure 2.1. Elements of a Sampled Data System Using Digital Processing

discrete amplitude levels (as in the ADC). In addition, the DAC output weights the signal output in the frequency domain thereby causing some signal distortion.

**Output Sampler** — One method of reducing the output frequency distortion is to resample the output signal using a very narrow sample width. The sampler takes the DAC held output and resamples it with narrow sample pulses.

**Reconstruction Filter** — Since the desired output signal is a continuous representation of the processed input signal, it is necessary to remove high frequency components resulting from the DAC or sampler outputs. This in effect smooths the analog output from sample to sample. A lowpass filter is used to perform the signal "reconstruction."

The process of sampling a signal introduces certain amounts of distortion called aliasing noise. The conversion of the analog samples to digital words is done with an analog to digital converter (ADC). This circuit represents the analog signal with a digital word which corresponds to a discrete amplitude approximation to the signal. This process also introduces a distortion term called quantization noise. By properly designing the sampled data system, these distortion or "noise" terms can be made insignificantly small so that the sampled data system closely represents the analog equivalent system with all the advantages of digital processing.

## 2.2 Sampling Theory

A digital signal processor requires the conversion of the input analog signal to a digital signal. Inherent in this analog-to-digital conversion is the sampling of the continuous input signal. As would be expected, the method and rate of sampling of the input signal affect the information content of the sampled signal so that some degree of distortion is incurred when the input signal is analog reconstructed from the digital data samples.

A sampling theorem that relates the minimum required sampling frequency to the signal bandwidth can be stated as follows. If a signal  $f(t)$  (a real function of time) is sampled instantaneously at regular intervals and at a rate higher than twice the signal bandwidth that includes all the significant frequency components, then the samples contain all the significant information of the original signal. The signal bandwidth, as used above, is the lowpass bandwidth for video signals and the RF bandwidth for signals modulated on a carrier.

Two aspects of the sampling theorem must be investigated prior to the selection of a sampling frequency.

- What is the effect of finite-width samples (vs instantaneous samples) on the information content of the samples?

- How is it determined that the signal bandwidth contains all significant frequency components?

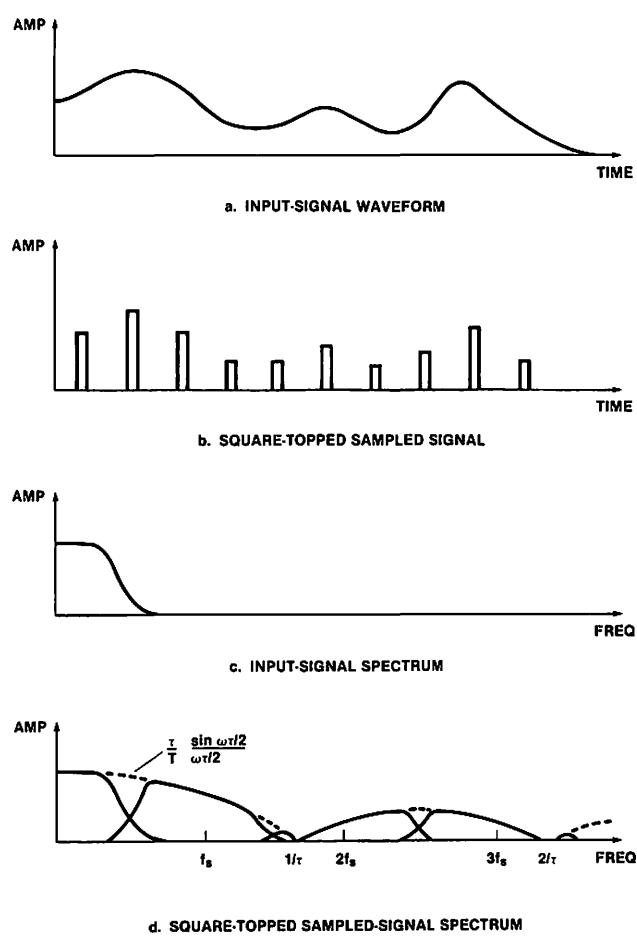

To digitize each sample, it is necessary that the sample pulse amplitude be constant during the sample to allow a digital word to be generated that represents the sampled analog value. This process is called "square-topped sampling" and can be realized using a sample-and-hold circuit. Because the 2920 works with digitized

samples, the square-topped sampling is the process of interest here.

Assuming an input spectrum  $F(j\omega)$ , the output spectrum for square-topped sampling  $F_{ST}(j\omega)$  is

$$F_{ST}(j\omega) = \left(\frac{\tau}{T}\right) \left(\frac{\sin(\omega\tau/2)}{\omega\tau/2}\right) \sum_{n=-\infty}^{\infty} F(j\omega - n\omega_s)$$

From this equation we note that the gain is a continuous function of frequency defined by

$$\left(\frac{\tau}{T}\right) \left(\frac{\sin(\omega\tau/2)}{\omega\tau/2}\right)$$

The time- and frequency-domain plots for the square-topped sampled signals are shown in Figure 2.2. It is clear in 2.2(d) that the sampling process acts as a low-pass filter with a  $\sin x/x$  amplitude response. If this filter response is not constant across the signal bandwidth, some information content of the signal will be lost due to rolloff distortion.

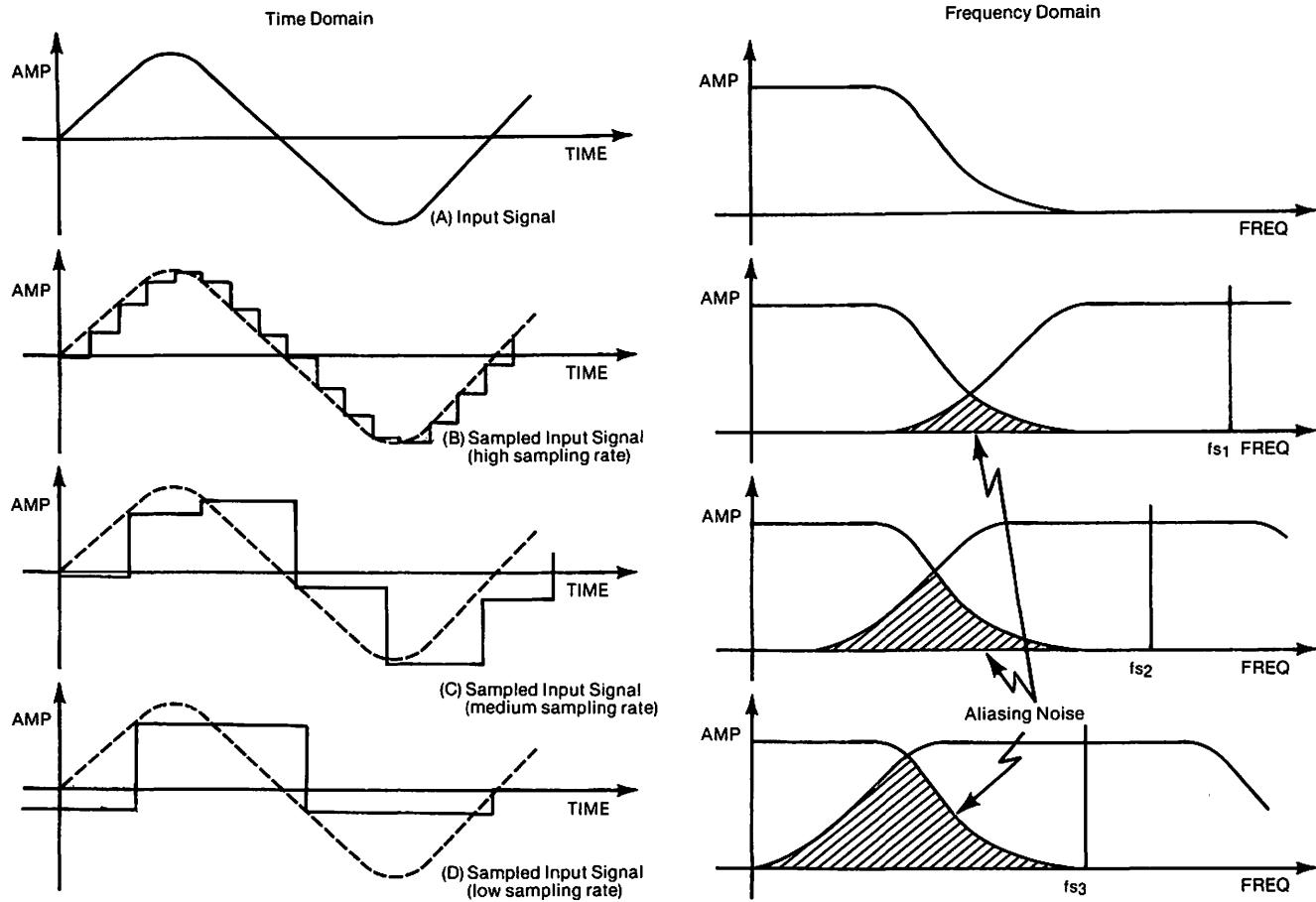

The amount of spectral overlap seen between the low-pass spectrum and that centered about the sampling frequency is referred to as aliasing noise. The effect of sample rate on aliasing noise for a given input spectrum can be clearly seen in Figure 2.3. Note that the amount of overlap increases as the sampling frequency is

Figure 2.2. Analysis of a Sampled Signal

Figure 2.3. Effects of Sampling Rate on Aliasing Noise

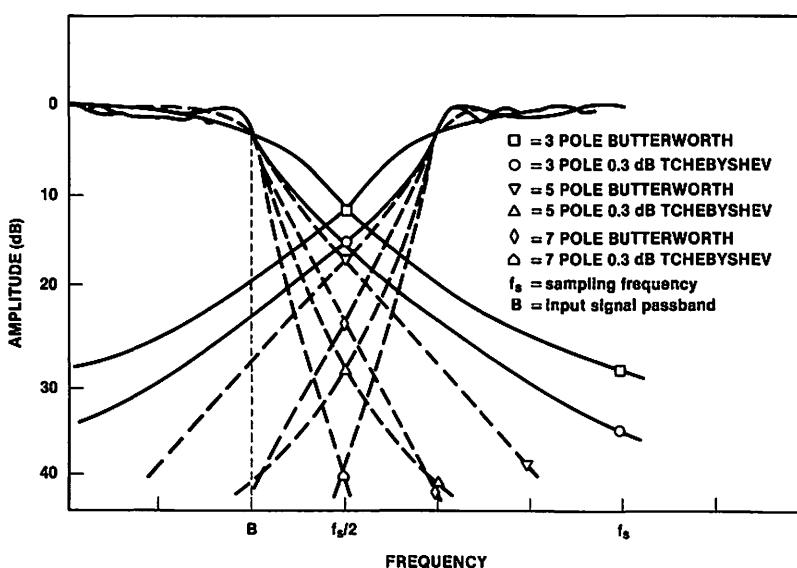

decreased. In a similar manner, for a fixed sampling frequency, the overlap could be reduced by increasing the filter rolloff before sampling (anti-aliasing filter). Figure

2.4 illustrates the overlap for several popular filter types. These tradeoffs between filter selectivity and sampling frequency will be used in the spectrum analyzer design.

Figure 2.4. Effects of Filtering on Aliasing Noise

### 2.3 Quantization Noise

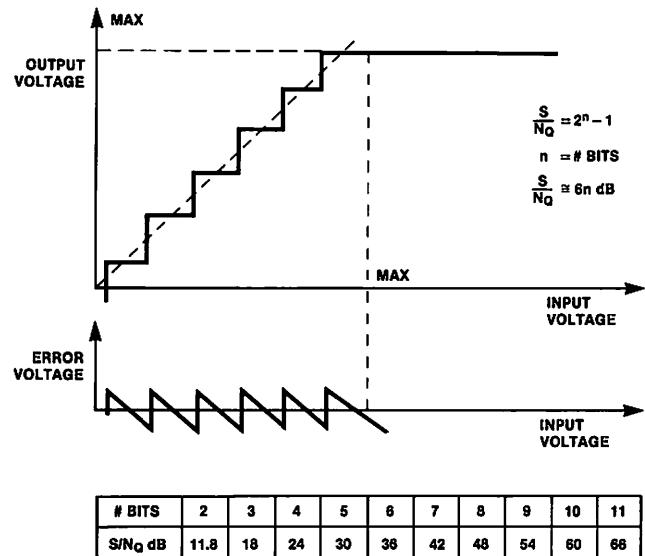

The analog-to-digital conversion of a signal implies that at specific times the signal is sampled and a digital word is formed that represents the amplitude of the signal at that time. The effect of the sampling process on the signal has been described, and it has been shown that a minimum loss of information is possible with the proper selection of bandwidths, sampling frequency, etc. The conversion from a continuous signal to a digital signal requires that the signal voltage be divided into  $M$  finite intervals which can be represented by an  $n$ -bit digital word, where

$$M = 2^n$$

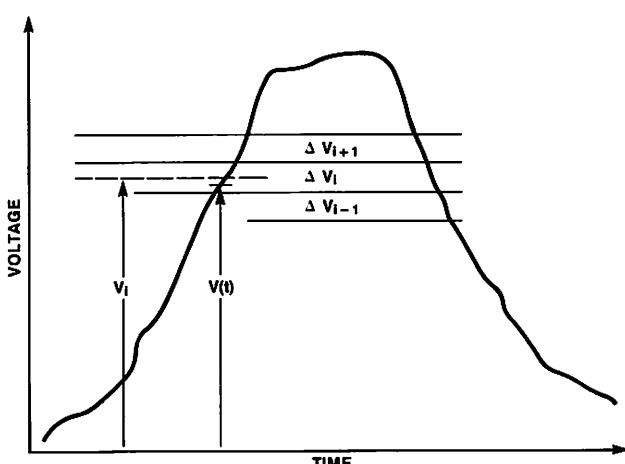

The quantizing error can be expressed in terms of the total mean squared error voltage between the exact and the quantized samples of the signal. With reference to Figure 2.5, a signal voltage  $V(t)$  falls between the  $i^{\text{th}}$  and the  $(i-1)^{\text{th}}$  levels which define the  $i^{\text{th}}$  quantizing interval. The error signal  $e_i$  is expressed as

$$e_i = V(t) - V_i$$

where

$e_i$  = error voltage between the exact and the  $i^{\text{th}}$  quantized voltage levels

$V(t)$  = input signal voltage

$V_i$  = voltage of the  $i^{\text{th}}$  quantized interval

Assuming uniform quantization and a uniform distribution of the signal voltage, the resulting signal to quantization noise ratio is found to be

$$S/N_Q = M^2 - 1$$

or represented as a logarithm

$$S/N_Q = (6)(n) \text{ dB}$$

where

$S$  is the peak signal power

$N_Q$  is the mean quantization noise

$M$  is the number of quantization levels =  $2^n$

$n$  is the number of bits in the amplitude word

Figure 2.5. Quantization Step

Figure 2.6 illustrates the error voltage due to quantization and the corresponding peak signal to quantization noise ratio as a function of the digital word length (number of bits).

Figure 2.6. Quantization Noise

### 2.4 Signal Reconstruction

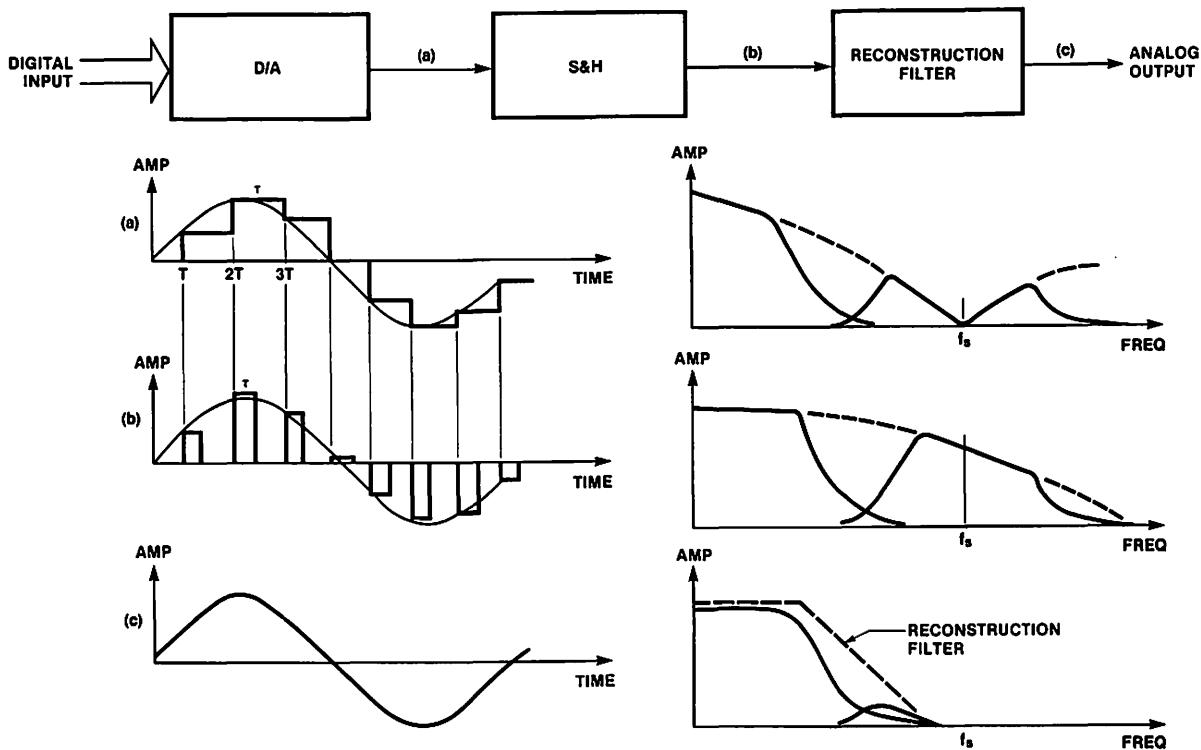

Signal reconstruction is the process that extracts the desired signal from the periodic samples at the output of the sampled data system. These samples may be the original samples at the output of the sample-and-hold or they may have been formed after linear or digital processing.

The basic assumption here is that a signal, which has been sampled and held for digital processing, is now to be converted back to analog form with minimum loss of information. The output of a sample-and-hold circuit (S&H) or a digital-to-analog converter (DAC) has a frequency spectrum as shown in Figure 2.7(a), where the sample width  $\tau$  is equal to the period of the sample  $T$ . The amplitude gain factor is observed to have a noticeable rolloff within the signal spectrum when the sampling period is a significant portion of the shortest signal period. This represents a distortion of the output signal and, unless it is compensated for, it will cause some loss of information similar to that of a lowpass filter with an insufficient bandwidth.

To correct this situation, either the reconstruction sampling pulse width should be made narrow relative to the inverse signal bandwidth  $1/B$ , or a  $\sin x/x$  correction is needed in the output filter. Figure 2.7(b) shows the effect of resampling with a narrower pulse.

As the sampling pulse width is made narrower, the amount of signal energy contained in the sampling pulses is reduced by an amount proportional to the duty cycle  $\tau/T$ . This gain reduction must be considered when analyzing the relative effects of fixed offsets, overshoot, ringing, and other spurious signals that degrade the desired signal.

Figure 2.7. Analog Signal Reconstruction

When the data samples have been established, they are passed through a reconstruction lowpass filter that removes the high-frequency components of the sampled signal (Figure 2.7(c)). The purpose of the output lowpass filter is primarily to remove the high-frequency spectra caused by the output sampling. It can also be used to help shape the amplitude and phase response of the output network. The Intel 2912 PCM line filter can sometimes be used for both anti-aliasing and signal reconstruction filtering. The 2912 reconstruction filter also provides  $\sin x/x$  correction.<sup>(1)</sup>

### 3.0 2920 SIGNAL PROCESSOR DESCRIPTION

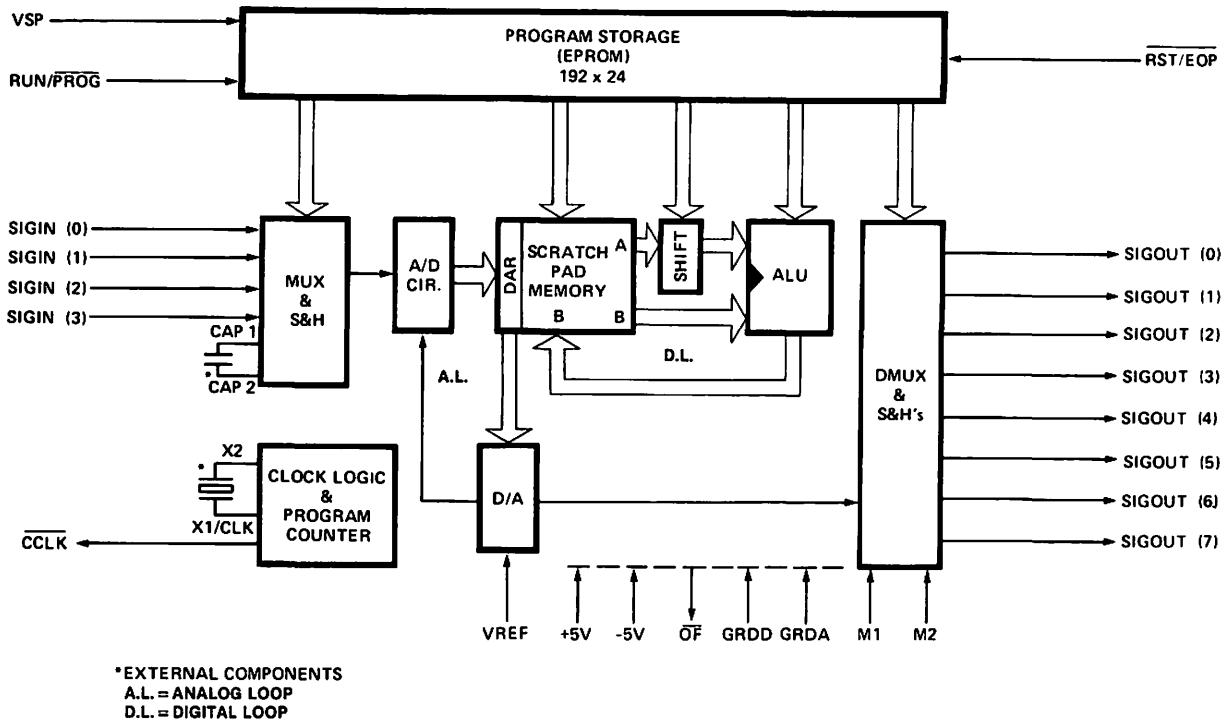

The 2920 performs all the functions illustrated in Figure 2.1 beginning with the input S&H and ending with the output S&H. In addition, 4 input lines and 8 output lines are multiplexed to give the 2920 the capability of realizing several circuits, or one circuit with multiple inputs and outputs. A functional block diagram of the 2920 is shown in Figure 3.1.

The functions of the 2920 are controlled by the instructions stored in its 192-word EPROM. Each instruction is 24 bits long and is split into 5 fields, with each field controlling a subsystem of the 2920. In order to maintain a constant sample rate, the execution time for each instruction is identical and there is no conditional branching. The sample rate is determined by the program length and the instruction cycle time, which is four clock cycles or 400 ns at the maximum 10 MHz clock

rate. A full 192 instruction program, running at 10 MHz, results in a 13 kHz sample rate. This allows for a signal bandwidth of approximately 4 kHz (maximum of 6.5 kHz with a rectangular filter). A shorter program will yield a higher sample rate.

#### 3.1 Analog Operations

The 2920 input and output operations are under program control. To acquire an input signal, one of the 4 input lines is selected and the signal sampled and held. The resulting sample is then converted to digital form using a successive approximation A/D conversion. The result of the conversion can be up to 9 bits (a sign bit and 8 amplitude bits). However, since the A/D conversion is under program control, the conversion could consist of only a single bit which might be used to read a logical input for example.

The result of the A/D conversion is stored in the DAR. This register provides the interface between the analog and digital sections of the 2920. After the A/D conversion, the digital word in the DAR can be moved to a scratch pad RAM location for further processing. The DAR is also used for the output operation where the 9 most significant bits of the value to be output are loaded into the DAR. The DAR drives the D/A converter, which is connected via the output demultiplexer to one of the 8 output S&H circuits.

#### 3.2 Digital Operations

The digital loop, shown in Figure 3.1, includes the 2 port, 40 word scratch pad RAM, a binary shifter, and the ALU. Two 25-bit words are fetched simultaneously from the 40 possible RAM locations. The data from the A port is

(1) R. E. Holm, "Data Conversion, Switching, and Transmission Using the Intel 2910A/2911A Codec and 2912 PCM Filter," Intel AP-64, p. 35.

Figure 3.1. Functional Block Diagram (Run Mode)

passed through the binary shifter, which allows scaling from  $2^2$  (a 2-bit left shift) to  $2^{-13}$  (a 13-bit right shift). The scaled A value and the unscaled B value are then passed on to the ALU. Sixteen internally available 4-bit constants are also accessible via the A port.

The ALU operates on the two values using the digital instructions specified by the program, and produces a 25-bit result. This result is then stored in the RAM location specified by the B address.

Digital and analog operations can execute simultaneously. For example, while doing a 9-bit A/D conversion, it is possible to implement a 5 pole lowpass filter with the digital section of the 2920. What gives the 2920 real-time processing capability is the ability to do the dual memory fetch, binary shift, ALU processing, and write back to memory as well as an analog operation in one instruction cycle (400 ns with a 10 MHz clock).

### 3.3 The 2920 Instruction Set

The following format is used by the 2920 assembler to specify the 24-bit instruction word stored in the EPROM:

| ALU INSTRUCTION | B ADDRESS (DESTINATION) | A ADDRESS (SOURCE) | SHIFT CODE | ANALOG INSTRUCTION |

|-----------------|-------------------------|--------------------|------------|--------------------|

|-----------------|-------------------------|--------------------|------------|--------------------|

Processing subsystems are implemented using a combination of analog and digital instructions.

The analog input and output instructions are IN(K) and OUT(K). To acquire a sample of the input signal, a sequence of IN(K) instructions is used. The A/D conversion is performed by the sign conversion and amplitude conversion instructions CVTS and CVT(K) respectively. A sequence of OUT(K) instructions will place a 9-bit amplitude on output channel K. Other analog instructions are the EOP instruction which resets the program counter to zero after the next three instructions are executed, NOP which is simply a no-operation, and CNDS or CND(K) which are conditional operators which test a bit of the DAR for the conditional ADD or LDA instruction, or define the destination of the carry bit for the conditional SUB instruction.

The arithmetic operations are ADD, SUB, and LDA which are addition, subtraction, and data transfer (load) respectively. These instructions may be modified with a conditional operator and used to perform multiplication or division by a variable or data dependent (conditional) switching. Other digital instructions are the absolute value ABS, the absolute value and add ABA, the ideal limit instruction LIM, and the logical instructions XOR and AND. Two special instructions, ABA CND( ) and XOR CND( ), are used to disable and enable, respectively, the ALU overflow saturation algorithm. The instruction set is given in Table 3.1. The 2920 internal constants and scalar mnemonics are listed in Table 3.2 and Table 3.3 respectively.

TABLE 3.1. INSTRUCTION SET AND OPERATIONS

| Mnemonics            |                          | Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                              |

|----------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Code                 | Condition                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                              |

| Digital Instructions |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                              |

|                      |                          | $(A \times 2^N) + B \rightarrow B^{[1]}$<br>$B - (A \times 2^N) \rightarrow B$<br>$(A \times 2^N) + 0 \rightarrow B$<br>$(A \times 2^N) \oplus B \rightarrow B$<br>$(A \times 2^N) \cdot B \rightarrow B$<br>$[(A \times 2^N)] \rightarrow B$<br>$[(A \times 2^N)] + B \rightarrow B$<br>$\text{Sign}(A) \rightarrow \pm \text{F.S.} \rightarrow B^{[4]}$<br>$(A \times 2^N) + B \rightarrow B$<br>$B \rightarrow B$<br>$B - (A \times 2^N) \rightarrow B$<br>$B + (A \times 2^N) \rightarrow B$<br>$(A \times 2^N) \rightarrow B$<br>$B \rightarrow B$ | $\text{IFF } \text{DAR}(K) = 1$<br>$\text{IFF } \text{DAR}(K) = 0$<br>$\& \text{ CY} \rightarrow \text{DAR}(K) \text{ IFF } \text{CY}_P = 1$<br>$\& \text{ CY} \rightarrow \text{DAR}(K) \text{ IFF } \text{CY}_P = 0$<br>$\text{IFF } \text{DAR}(K) = 1$<br>$\text{IFF } \text{DAR}(K) = 0$ |

| ADD                  | CND( ) <sup>[2]</sup>    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                              |

| SUB                  | CND( ) <sup>[2][7]</sup> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                              |

| LDA <sup>[3]</sup>   |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                              |

| XOR <sup>[3]</sup>   |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                              |

| AND                  |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                              |

| ABS <sup>[3]</sup>   |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                              |

| ABA                  |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                              |

| LIM                  |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                              |

| ADD                  | CND( ) <sup>[2]</sup>    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                              |

| SUB                  | CND( ) <sup>[2][7]</sup> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                              |

| LDA                  | CND( ) <sup>[2]</sup>    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                              |

| ABA                  | CND( ) <sup>[8]</sup>    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                              |

| XOR                  | CND( ) <sup>[8]</sup>    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                              |

| Analog Instructions  |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                              |

| IN(K)                |                          | Signal Sample from Input Channel K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                              |

| OUT(K)               |                          | D/A to Output Channel K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                              |

| CVTS                 |                          | Determine Sign Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                              |

| CVT(K)               |                          | Perform A/D on Bit K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                              |

| EOP                  |                          | Program Counter to Zero <sup>[6]</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                              |

| NOP                  |                          | No Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                              |

| CND(K)               |                          | Select Bit K for Conditional Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                              |

| CNDS                 |                          | Select Sign Bit for Conditional Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                              |

Notes:

1. Note that scaling of A always occurs before executing the digital operation.

2. CND( ) can be either CND(K) or CNDS testing amplitude bits or the sign bit of the DAR respectively.

3. Clarification of CY<sub>OUT</sub> sense for certain operations. For LDA, XOR, AND, ABS: CY<sub>OUT</sub> → 0.

4. B is set to full scale (F.S.) amplitude with the same sign as the "A" port operand.

5. The previous carry bit (CY<sub>P</sub>) is tested to determine the operation. The present carry bit (CY) is loaded into the Kth bit location of the DAR. "Present carry (CY) is generated independent of overflow. It will represent the carry (CY) of a calculated 28-bit result."

6. EOP will also enable overflow correction if it was disabled during a program pass. The EOP must occur in ROM location 188.

7. For SUB CNDS operation CY → DAR(S).

8. Does not affect DAR. In this case, CND is used with XOR/ABA to enable/disable the ALU overflow saturation algorithm. Use of either instruction causes the ALU output to roll over rather than go to full scale with sign bit preserved. An EOP instruction will also enable the ALU overflow saturation algorithm.

TABLE 3.2. CONSTANT MNEMONICS

| Mnemonic | Value  | Bit Sequence |

|----------|--------|--------------|

| KP0      | 0.000  | 0.000        |

| KP1      | 0.125  | 0.001        |

| KP2      | 0.25   | 0.010        |

| KP3      | 0.375  | 0.011        |

| KP4      | 0.5    | 0.100        |

| KP5      | 0.625  | 0.101        |

| KP6      | 0.75   | 0.110        |

| KP7      | 0.875  | 0.111        |

| KM1      | -0.125 | 1.111        |

| KM2      | -0.25  | 1.110        |

| KM3      | -0.375 | 1.101        |

| KM4      | -0.5   | 1.100        |

| KM5      | -0.625 | 1.011        |

| KM6      | -0.75  | 1.010        |

| KM7      | -0.875 | 1.001        |

| KM8      | -1.0   | 1.000        |

The 2920 Assembler accepts these mnemonics as inputs to specify the 4-bit sequences shown in Table 3.2. These constants are stored as read only "RAM" locations in the 2920. The binary point is placed to the right of the most significant bit (MSB). Longer bit patterns may be obtained by shifting and adding several constants. A right shift operation in the 2920 fills the left most bit positions with the sign bit (0 for positive constants, 1 for negative constants). Negative constants are represented in 2's complement notation.

TABLE 3.3. SCALER MNEMONICS

| Scaler Mnemonic | Equivalent Multiplier | Scaler Mnemonic | Equivalent Multiplier       |

|-----------------|-----------------------|-----------------|-----------------------------|

| L02             | $2^2 = 4.0$           | R06             | $2^{-6} = 0.015625$         |

| L01             | $2^1 = 2.0$           | R07             | $2^{-7} = 0.0078125$        |

| R00             | $2^0 = 1.0$           | R08             | $2^{-8} = 0.00390625$       |

| R01             | $2^{-1} = 0.5$        | R09             | $2^{-9} = 0.001953125$      |

| R02             | $2^{-2} = 0.25$       | R10             | $2^{-10} = 0.0009765625$    |

| R03             | $2^{-3} = 0.125$      | R11             | $2^{-11} = 0.00048828125$   |

| R04             | $2^{-4} = 0.0625$     | R12             | $2^{-12} = 0.000244140625$  |

| R05             | $2^{-5} = 0.03125$    | R13             | $2^{-13} = 0.0001220703125$ |

## 4.0 DESCRIPTION OF SPECTRUM ANALYZER

The purpose of this spectrum analyzer is to determine the long term spectral characteristics of a signal in the 200 Hz to 3.2 kHz frequency band. The approach used is to sweep the input signal through a high resolution (narrowband) bandpass filter and observe the filter response as a function of the frequency sweep. First the spectrum analyzer block diagram and parameters are determined. Then sampled data considerations are taken into account, and finally the 2920 signal processor code is developed in Section 5.0.

### 4.1 Specifications

A spectrum analyzer which covers the audio frequency range of 200 Hz to 3.2 kHz was selected for this design. The specifications of the analyzer are given in Table 4.1.

TABLE 4.1 SPECTRUM ANALYZER SPECIFICATIONS

- INPUT BANDWIDTH: 3 kHz

- RESOLUTION BANDWIDTH: 100 Hz

- SWEEP RATE: 6 kHz/sec or 0.5 sec/Band

- DYNAMIC RANGE: 48 dB

- INPUTS — ANALOG SIGNAL:  $-1V \leq \text{SIG} \leq 1V$

- OUTPUTS — FREQUENCY RESPONSE LINEAR AMPLITUDE (VERTICAL AXIS)

- FREQUENCY RESPONSE LOG AMPLITUDE (VERTICAL AXIS)

- SWEEP WAVEFORM (SAWTOOTH) (HORIZONTAL AXIS)

- OPTIONAL OUTPUTS — VCO (SWEEPING SINUSOID)

### 4.2 Block Diagram Description

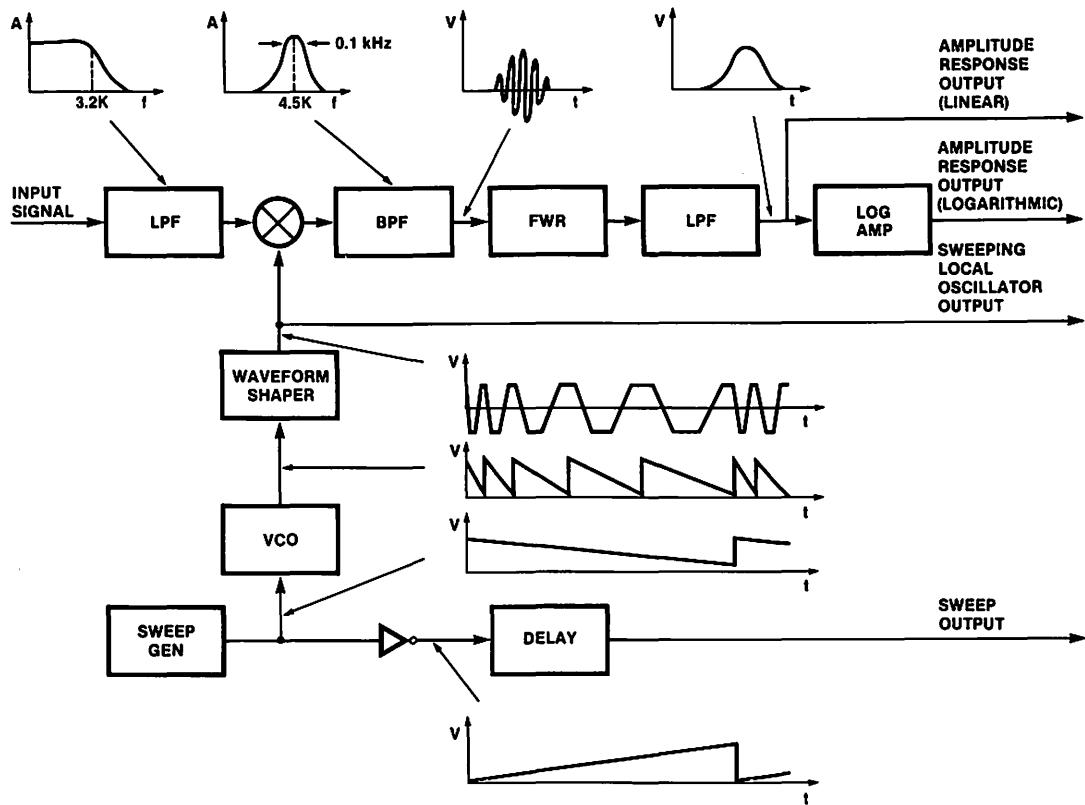

Ideally, a scanning spectrum analyzer could be implemented by simply scanning a tunable narrowband bandpass filter across the input signal band to determine the signal energy at any frequency. Practically speaking it is nearly impossible to design a complex tunable analog filter which can cover a 10 to 1 range of frequencies, especially near DC. Even digital implementations become very complex and hardware inefficient when tuning is required. It is therefore easier to realize the equivalent of the scanning filter by sweeping the signal past a fixed tuned narrowband bandpass filter. This is accomplished by the superheterodyne system illustrated in the block diagram of Figure 4.1.

**Additional Functions** — The block diagram in Figure 4.1 shows the basic functions or subsystems which must be implemented to operate the spectrum analyzer. In the digital implementation there must also be an input anti-aliasing filter, sample and hold, A/D converter, and the corresponding output D/A converter and reconstruction filter. The analog-digital functions are implemented by a single 2920 signal processor in software.

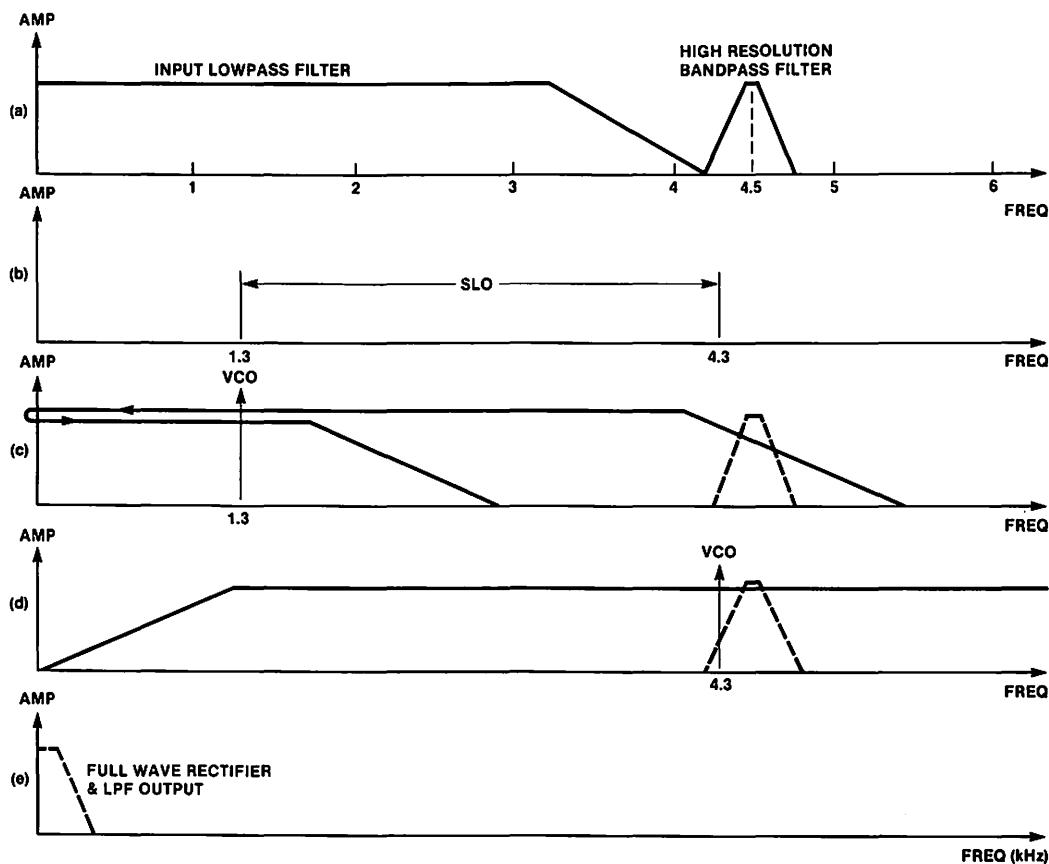

**Block Diagram** — The input signal spectrum is first shaped by the input lowpass filter (LPF) (in addition to the anti-aliasing filter shaping) to avoid overlapping spectral components after mixing. The filtered signal then is multiplied (mixed) by the sweeping local oscillator (SLO) to generate upper and lower sidebands centered about the SLO frequency. The spectral characteristics of the system are shown in Figure 4.2. The bandpass filter (BPF) is centered at 4.5 kHz with a 100 Hz bandwidth. Figure 4.2(a) shows the filter characteristics. The SLO sweeps from 1.3 kHz to 4.3 kHz as seen in Figure 4.2(b). After mixing, the upper and lower sidebands are seen in Figures 4.2(c) and (d) for SLO frequencies of 1.3 and 4.3 kHz respectively. Only the upper sideband is of interest however as it is swept across the BPF and the signal energy is extracted. When the SLO is at 1.3 kHz the BPF is looking at the high band (3.2 kHz). As the SLO frequency increases, the apparent signal frequency seen by the BPF decreases until at a SLO frequency of 4.3 kHz, the BPF "sees" the signal energy at 200 Hz (4.5 kHz minus 4.3 kHz).

The block diagram shows that the BPF output is then passed through a full wave rectifier (FWR) and lowpass filter to extract the envelope from the 4.5 kHz carrier which is generated when signal energy is present. The resulting signal spectrum is centered at DC and shown in Figure 4.2(e).

The sweep output provides a horizontal sweep voltage for an X-Y display. The purpose of the delay shown in Figure 4.1 is to synchronize the sweep output with the amplitude response output. This delay should approximately equal the propagation delays of the BPF and output LPF.

**I/O** — The input to the spectrum analyzer is the analog signal to be analyzed. There are several outputs identified in Figure 4.1. These include the frequency sweep output which becomes the horizontal axis drive to a scope, the VCO output, and the BPF amplitude response (both linear and logarithmic) output which becomes the vertical axis drive to the scope.

### 4.3 Sampled Data System Considerations

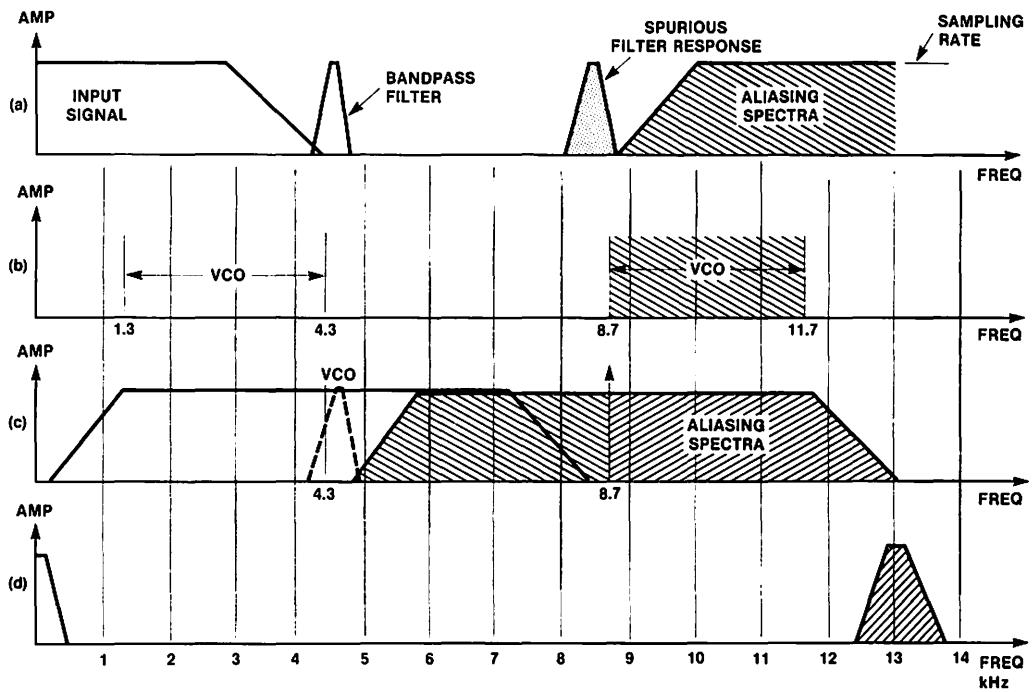

An expansion of the frequency axis in Figure 4.2 to include the sampling frequency at 13 kHz shows the first order aliasing spectra as seen in Figure 4.3. From this figure the limitations and requirements for filter rolloff, bandwidths, and center frequencies become clearer.

Figure 4.1. Spectrum Analyzer Block Diagram

Figure 4.2. Frequency Domain Analysis of Spectrum Analyzer

Figure 4.3. Frequency Domain Analysis of Sampled Data Spectrum Analyzer

**Bandpass Filter** — The location of the bandpass filter is determined by the input lowpass filter bandwidth and rolloff (Figure 4.3(a)) and the aliased spectrum of the lower sideband resulting when the SLO is at 4.3 kHz (Figure 4.3(c)). The BPF must have enough rolloff to eliminate both the baseband and aliased out-of-band signal components that are present. Analysis shows that a 3 pole pair Bessel filter will suffice if the input LPF is designed properly. The Bessel filter also has ideal transient response (no overshoot) so that the resulting output will not have overshoot and ringing.

**Input LPF** — This filter determines not only the baseband (centered about DC) spectrum but also that of the aliased lower sideband of the SLO. It was found that a 4 pole, 2 zero filter provides adequate rolloff to keep spurious signal (and aliased) components of significant amplitude (less than 48 dB down) out of the BPF passband.

**Output LPF** — This filter is used to remove the harmonic content of the FWR output (and the associated aliased components) before the signal is converted back to analog and outputted.

## 5.0 DESCRIPTION OF SUBSYSTEM IMPLEMENTATION

This section develops 2920 assembly code for several subsystems of the spectrum analyzer and discusses various aspects of the total program. The instruction set is given in Section 3 as well as a description of the 2920 device. The digitally implemented subsystems described here are: (1) sweep rate generator and SLO, (2) multiplier, (3) output lowpass filter, and (4) log amplifier. These are discussed following a discussion of the input anti-aliasing filter.

### 5.1 Anti-aliasing Filter

The basic function of the anti-aliasing filter is to attenuate the out-of-band spectral components of the input signal in order to reduce the effects of aliasing. From Figure 4.3 it is seen that with a 13 kHz sampling frequency (corresponding to a full 2920 program and a 10 MHz clock) the aliasing components must be below -50 dB at 3.2 kHz or 9.8 kHz from the sampling frequency. Therefore, the anti-aliasing filter attenuation characteristics are: (1) relatively little rolloff by 3.2 kHz (say 1 dB) and (2) 50 dB by 9.8 kHz. Filter curves (readily available in the literature) show that this would require a 6 pole Butterworth, or a 5 pole 0.5 dB ripple Tchebyshev, or equivalent.

Note that this filter is only needed if the input signal has significant frequency components above about 7 kHz. If a controlled signal is to be processed by the spectrum analyzer (such as sine waves or narrowband signals) then an anti-aliasing filter may not be needed.

### 5.2. Sweep Rate Generator (SRG) and Sweeping Local Oscillator (SLO)

Development of the SRG and SLO are good examples of using time domain processing to avoid some of the problems which result from nonlinear processes creating aliasing components within the sampled system and beyond the help of an anti-aliasing filter. The purpose of the SRG is to provide the horizontal sweep output for an oscilloscope and to create an input to a voltage controlled oscillator (VCO) which will result in a linear frequency sweep as a function of time. The SLO is then a combination of the SRG and VCO, e.g. the sawtooth wave of the SRG drives the VCO resulting in a linear sweeping local oscillator which sweeps between

predetermined frequencies (1.3 kHz and 4.3 kHz) with a sweep rate determined by the period of the sawtooth wave.

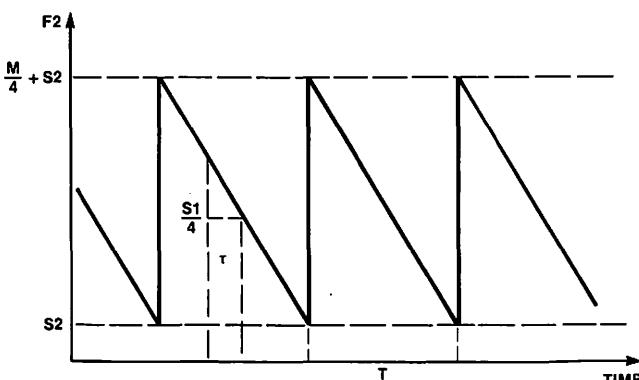

**Sweep Rate Generator** — A sawtooth wave with an offset is the required output of this subsystem. The slope of the sawtooth determines the rate of change of frequency of the VCO, the voltage excursion is proportional to the frequency range of the VCO, and the offset represents the minimum frequency. As an output signal, the sawtooth provides a linear sweep for the horizontal axis of a scope (X-Y display) which is synchronized with the frequency sweep of the VCO. Based on the input specifications, a repetition rate of 2 sweeps/sec is needed.

The sawtooth wave is simply generated by continuously decrementing a register with a fixed value and thereby generating a linear negative slope. When the voltage changes sign (crosses zero) a constant equal to the sawtooth peak amplitude is added. This is accomplished by using an add (ADD) instruction conditioned on the sign bit. Once the sawtooth waveform is generated, it is scaled and a constant offset is added to provide a minimum voltage corresponding to the minimum frequency of the VCO. The resulting waveform and the 2920 program to generate this function is shown in Figure 5.1. Because of the low frequency of this signal (2.0 Hz) compared to the sampling frequency (13 kHz), all aliasing components are negligible. Therefore no action is needed to control them.

The program of Figure 5.1 presupposes the existence of two constants S1 and S2. These constants must be generated by the program prior to their use. Since each constant represents a sequence of ones and zeros, they can be generated several ways. One is to use a combination of shifts and adds of the constants KP<sub>x</sub> or KM<sub>x</sub> (see Section 3) to the register S1 or S2. Another approach is to read in a value from outside the chip by performing an A/D conversion of a DC voltage. This would allow both

the sweep rate and the frequency range to be controlled externally. Figure 5.2 gives an example of creating the constant S1.

ASSUME FROM FIGURE 5.1 THAT

$$\begin{aligned} \tau &= 76.8 \mu\text{sec} \\ M &= 1.0 \text{ VOLT} \\ T &= 0.5 \text{ sec} \end{aligned}$$

$$\text{THEN } S1 = \frac{M}{(\tau/T)} = 15.36 \times 10^{-5} \text{ VOLTS STEP}$$

CONVERTING TO BINARY YIELDS

$$\begin{aligned} S1 &= 15.36 \times 10^{-5} = 2^{-13} + 2^{-15} + 2^{-20} \\ &= (2^{-1} + 2^{-3} + 2^{-8})2^{-12} \\ &= (0.10100001)2^{-12} \end{aligned}$$

WE SEE THAT BY SPLITTING THE BINARY WORD INTO GROUPS OF 4 BITS YIELDS

$$S1 = [0.101] + [0.001]2^{-5}2^{-12}$$

FROM SECTION 3.0 TABLE 3.2 THIS EQUALS [KP5 + KP1 × 2<sup>-5</sup>] × 2<sup>-12</sup> OR IN 2920 ASSEMBLY LANGUAGE

| OP  | DEST | SOURCE | SHF | COND |

|-----|------|--------|-----|------|

| LDA | S1   | KP5    | R00 | —    |

| ADD | S1   | KP1    | R05 | —    |

| LDA | S1   | S1     | R12 | —    |

LESS THAN ONE PERCENT ERROR IN THE SWEEP RATE IS INTRODUCED BY NEGLECTING KP1 R05. THEREFORE, 2 PROGRAM STEPS CAN BE SAVED AND THE CONSTANT CAN BE GENERATED WITH A SINGLE INSTRUCTION

LDA S1 KP5 R12

Figure 5.2. Developing the Constant S1 in the 2920

**Voltage Controlled Oscillator** — The VCO is developed in the same way as the SRG except that the decrement value is not a constant but rather is determined by a scaled version of the SRG input waveform. The calculation would be the same as shown in Figure 5.2 for both ends of the VCO frequency range. An offset would be determined by the low frequency and the scaling factor by the high frequency. The net result would be a sawtooth wave with a varying period as a function of time.

This high frequency sawtooth wave (1.3 kHz to 4.3 kHz) has significant harmonic content which will be reflected by the sampling frequency harmonics and cause distortion of the desired input to the mixer. Digital filters cannot be used here because they are susceptible to the aliasing components also. Some means must therefore be found to reduce the harmonic content of this signal. One approach would be to filter the VCO output using an external filter. This would involve additional hardware plus many extra instructions for I/O and A/D conversion. An alternative is to shape the waveform in the time domain to look more like the desired sinusoid.

By investigating the Fourier Transforms of various symmetric waveforms it is noticed that a trapezoidal waveform can be adjusted so that even harmonics are eliminated and the first odd harmonic is the fifth. This is done by selecting the top of the trapezoid to be 2/3 of the peak of a corresponding triangle wave. The program to accomplish this transformation is shown in Figure 5.3.

Figure 5.1. VCO Input Waveform and 2920 Program Example

| OP  | DEST | SOURCE | SHF | COND | COMMENTS                                                                                                                   |

|-----|------|--------|-----|------|----------------------------------------------------------------------------------------------------------------------------|

| SUB | OSC1 | F2     | R00 | —    | WAVEFORM SHAPING                                                                                                           |

| LDA | DAR  | OSC1   | R00 | —    |                                                                                                                            |

| ADD | OSC1 | M      | R00 | CNDS |                                                                                                                            |

| LDA | OSC  | OSC1   | R00 | —    |                                                                                                                            |

| SUB | OSC  | M      | R01 | —    |                                                                                                                            |

| ABS | OSC  | OSC    | L01 | —    |                                                                                                                            |

| SUB | OSC  | M      | R01 | —    | DOUBLE & TAKE ABS VALUE                                                                                                    |

| ADD | OSC  | OSC    | L01 | —    | RECENTER ABOUT 0                                                                                                           |

|     |      |        |     |      | MULTIPLY BY 3. IF WE SET M = 1 THEN WAVEFORM WILL TRY TO REACH 1.5 AND WILL LIMIT AT 1 (60°) WHICH MINIMIZES 3RD HARMONICS |

DEFINITIONS

F1 = SAWTOOTH WAVE VOLTAGE = SOURCE OF VARIABLE STEP SIZE TO SLO

M = CONSTANT VALUE < 1.0

S2 = MINIMUM STEP SIZE FOR SLO

F2 =  $F1/4 + S2$  = SLO STEP SIZE

OSC1 = BASIC SLO OUTPUT BUT WITH VARIABLE FREQ SAWTOOTH WAVE

OSC = FINAL SLO OUTPUT AFTER WAVESHAPING

SWEEP RATE =  $\frac{S2}{T} < RATE < \frac{M/4 + S2}{T}$

T = SAMPLE PERIOD

Figure 5.3. Sweeping Local Oscillator (SLO) Program

### 5.3 Implementation of a 4 Quadrant Multiplier

The mixer shown in Figure 4.1 which multiplies the filtered input signal times the SLO waveform must be implemented as a 4 quadrant multiply since both waveforms have positive and negative values. A microprocessor implementation of this multiply might use a shift and add algorithm to determine the magnitude of the product and separate logic to determine the sign. A more direct algorithm is used in the 2920 to avoid the necessity of dealing with the sign bit separately.

**Number Representation** — It is convenient to form a representation of a number in 2's complement notation since this notation is hardware efficient and is used in the 2920. Assume that X is the multiplier number (sign and magnitude) and Y is the multiplicand. We can represent X in 2's complement as

$$\begin{aligned}

X &= (-1)s + s \sum_{i=0}^n \bar{b}_i 2^{-i} + \bar{s} \sum_{i=0}^n b_i 2^{-i} + s 2^{-n} \\

&= s \left[ -1 + \sum_{i=0}^n \bar{b}_i 2^{-i} + 2^{-n} \right] + \bar{s} \sum_{i=0}^n b_i 2^{-i}

\end{aligned}$$

where s is the sign bit; 0 is positive, 1 is negative

$b_i$  is the weighting and is either 1 or 0

This can be rewritten as

$$X = -s + x$$

where x represents the magnitude of the amplitude bits excluding the sign bit.

$$X = \sum_{i=0}^n \bar{b}_i 2^{-i} + 2^{-n} \quad \text{for } X < 0$$

$s = 1$

$$X = \sum_{i=0}^n b_i 2^{-i} \quad \text{for } X \geq 0$$

$s = 0$

**Product Implementation** — The product,  $Z = X \times Y$ , can now be determined as follows:

LET  $X = (s, x) = -s + x$

$Y = (t, y) = -t + y$

WHERE  $s = \text{SIGN BIT OF } X$

$t = \text{SIGN BIT OF } Y$

$x = \text{MAGNITUDE OF } X$

$y = \text{MAGNITUDE OF } Y$

THEN  $Z = X \cdot Y$

$= (-s + x)(-t + y)$

$= st + xy - sy - tx$

Now the 2920 can easily implement the product of a positive multiplier and a bipolar multiplicand using a simple shift and conditional add algorithm. The add is conditioned on the value of the multiplier bit located in the DAR.

IF THE SIGN BIT IS IGNORED IN THE MULTIPLIER, X, THE RESULTING PRODUCT WILL BE

$$\begin{aligned} Z' &= (x)(-t + y) \\ &= xt + xy \end{aligned}$$

THIS EXPRESSION LACKS THE TERMS

$$st - sy = s(-Y)$$

WHICH CAN BE ADDED TO FORM THE ENTIRE PRODUCT

$Z = Z' + s(-Y)$  BY PERFORMING A CONDITIONAL

ADD OF  $-Y$  BASED ON THE VALUE OF "s."

The resulting 2920 Assembly code is shown in Figure 5.4 along with comments.

| OP                         | DEST | SOURCE | SHF | COND  | COMMENTS                                                            |

|----------------------------|------|--------|-----|-------|---------------------------------------------------------------------|

| LDA                        | DAR  | X      | R00 | —     | SET UP DAR FOR CONDITIONAL ADD'S, X IS MULTIPLIER                   |

| ADD                        | Z    | Y      | R01 | CND 7 |                                                                     |

| ADD                        | Z    | Y      | R02 | CND 6 |                                                                     |

| ADD                        | Z    | Y      | R03 | CND 5 |                                                                     |

| ADD                        | Z    | Y      | R04 | CND 4 |                                                                     |

| ADD                        | Z    | Y      | R05 | CND 3 |                                                                     |

| ADD                        | Z    | Y      | R06 | CND 2 |                                                                     |

| ADD                        | Z    | Y      | R07 | CND 1 |                                                                     |

| ADD                        | Z    | Y      | R08 | CND 0 |                                                                     |

| SUB                        | Y    | Y      | L01 | —     | MULTIPLY Y BY THE MAGNITUDE OF X, THAT IS $x$ WHERE $Z = x(-t + y)$ |

| DEVELOP -Y                 |      |        |     |       |                                                                     |

| Y $\leftarrow Y - 2Y = -Y$ |      |        |     |       |                                                                     |

| ADD                        | Z    | Y      | R00 | CNDS  | CONDITIONAL ADD OF $-Y$ IF SIGN OF X IS NEGATIVE                    |

| SUB                        | Y    | Y      | L01 | —     | RESTORES ORIGINAL SIGN OF Y IF NEEDED                               |

Figure 5.4. 4 Quadrant Multiply Program

#### 5.4 Design and Implementation of the Output Lowpass Filter

The primary purpose of the output lowpass filter is to eliminate the harmonic content of the full wave rectifier (FWR) output and the corresponding aliased components. The filter passband must be at least half that of the narrowband BPF (preferably wider) and the filter complexity should be minimized to reduce amplitude/phase distortion of the signal and ease implementation.

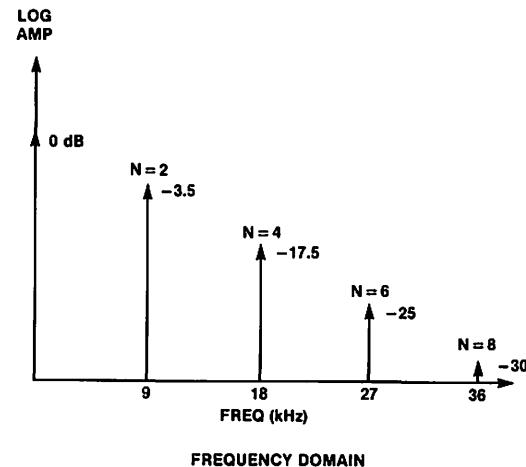

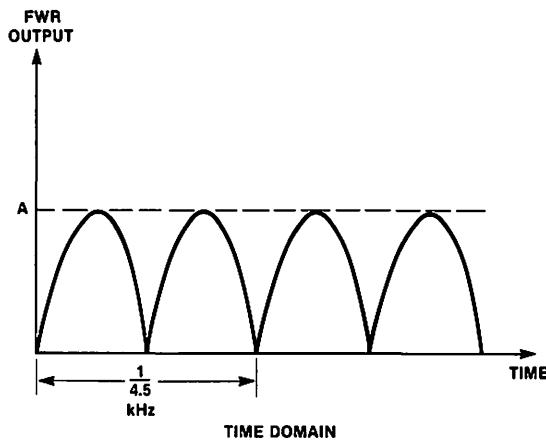

**Design Considerations** — The FWR spectral output is shown in Figure 5.5 along with the corresponding time domain waveform assuming quasi-static amplitude variation (relatively little change in amplitude over several 4.5 kHz carrier cycles). The desired signal information is located from DC to 50 Hz. All other signal components should be removed by filtering.

The spectral components illustrated in Figure 5.5 will also be centered about multiples of the sampling frequencies (aliasing noise) and must be considered before selecting a filter. This process is tabulated in Table 5.1 where  $\Delta f = |Mf_s - Nf_{FWR}|$ , N is the FWR harmonic, M is the sampling frequency harmonic and the  $\Delta f$  amplitude is determined by N from Figure 5.5.

From Table 5.1 it is clear that the 1 kHz component (N = 6, M = 2) is the most critical since it is closest to the filter passband and also requires a full 25 dB of attenuation by the filter. The 4 kHz component (N = 2, M = 1) requiring 46.5 dB must also be considered.

A look at the attenuation characteristics of standard filters shows that both criteria are met with a 2 pole Butterworth filter with a bandwidth of 50 Hz.

Figure 5.5. Harmonic Analysis of the Full Wave Rectifier (FWR)

TABLE 5.1. ALIASING COMPONENTS OF FWR OUTPUT

| FWR <sup>1</sup> HARMONIC N | $f_s^2$ <sup>2</sup> HARMONIC M | ALIAS <sup>3</sup> FREQ (kHz) | AMPLITUDE <sup>4</sup> LEVEL OF COMPONENT | ATTN REQ'D (to reach 50 dB) |

|-----------------------------|---------------------------------|-------------------------------|-------------------------------------------|-----------------------------|

| 2                           | 1                               | 4                             | -3.5 dB                                   | 46.5 dB                     |

|                             | 2                               | 17                            |                                           |                             |

|                             | 3                               | 30                            |                                           |                             |

|                             | 4                               | 43                            |                                           |                             |

| 4                           | 1                               | -5                            | -17.5 dB                                  | 37.5 dB                     |

|                             | 2                               | 8                             |                                           |                             |

|                             | 3                               | 21                            |                                           |                             |

|                             | 4                               | 34                            |                                           |                             |

| 6                           | 1                               | -14                           | -25 dB                                    | 25 dB                       |

|                             | 2                               | -1                            |                                           |                             |

|                             | 3                               | 12                            |                                           |                             |

|                             | 4                               | 25                            |                                           |                             |

| 8                           | 1                               | -23                           | -30 dB                                    | 20 dB                       |

|                             | 2                               | -10                           |                                           |                             |

|                             | 3                               | 3                             |                                           |                             |

|                             | 4                               | 16                            |                                           |                             |

| 10                          | 1                               | -32                           | -34 dB                                    | 16 dB                       |

|                             | 2                               | -19                           |                                           |                             |

|                             | 3                               | 6                             |                                           |                             |

|                             | 4                               | 7                             |                                           |                             |

| 12                          | 1                               | -41                           | -37 dB                                    | 13 dB                       |

|                             | 2                               | -28                           |                                           |                             |

|                             | 3                               | -15                           |                                           |                             |

|                             | 4                               | -2                            |                                           |                             |

1. FWR Fundamental is 4.5 kHz.

2. Sample frequency is 13 kHz.

3. The alias frequency is the absolute value of the value shown. Negative frequencies fold around DC to become positive.

4. Determined from spectrum of FWR output (Figure 5.5).

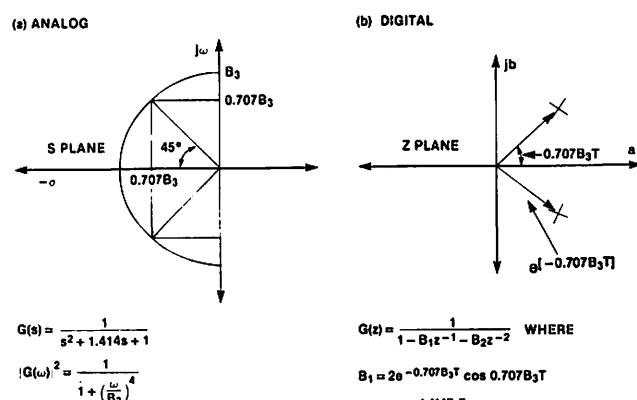

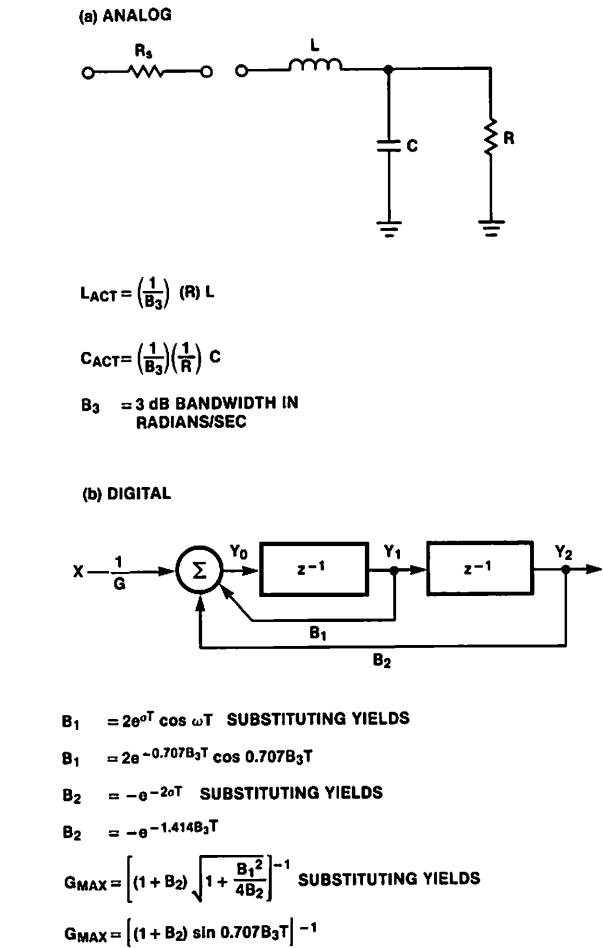

**Filter Implementation** — The transfer function and s-plane pole-zero plot of the 2 pole Butterworth lowpass filter are shown in Figure 5.6(a) as a function of the 3 dB bandwidth  $B_3$ . Figure 5.7(a) shows a lumped parameter LC filter realization of this transfer function where L, C, and R are normalized lowpass prototype values which must be scaled by the actual resistive load and bandwidth of the filter. An approximation to this filter can be implemented digitally using the 2920 once the conversion from analog to digital or from s-plane to z-plane is performed.

The matched z-transform is defined as  $z = e^{st}$  where s is a complex frequency defined by its real and imaginary parts (see Figure 5.6(a)) and T is the sample period of the

sampled data system (the 2920 in this case). Expanding s into its components yields  $z = e^{(\sigma T \pm j\omega T)} = e^{\sigma T} e^{\pm j\omega T}$  where  $\sigma$  is the real part and  $\omega$  is the imaginary part of s. This final expression is recognized as a magnitude and a phase which is plotted in Figure 5.6(b) for the 2 pole Butterworth case ( $|\sigma| = |\omega| = 0.707B_3$ ). The real and imaginary parts of z can now be calculated and the resulting z transform transfer function G(z) determined as seen in Figure 5.6(b).

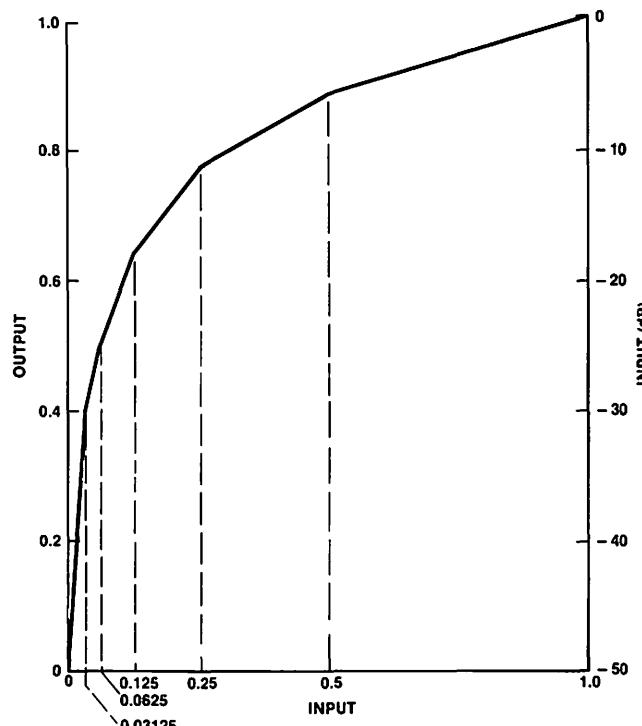

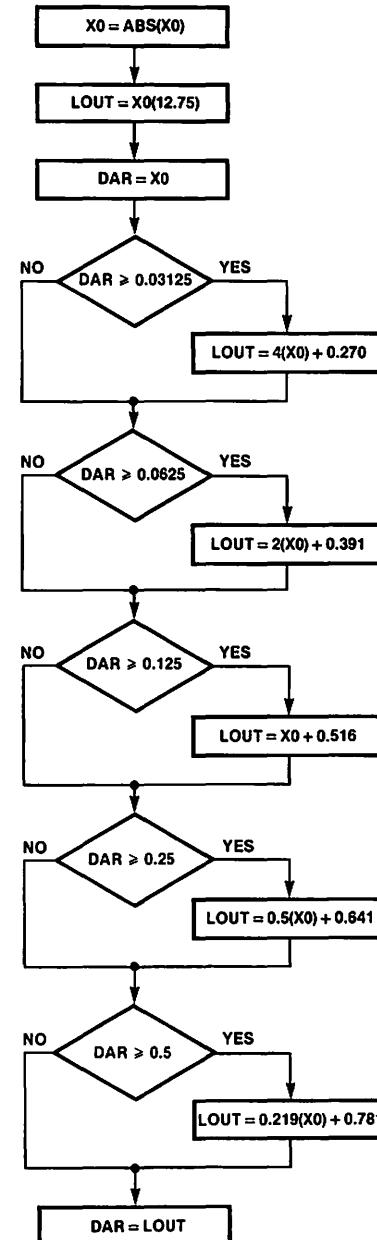

The transfer function G(z) can be realized digitally with the 2 stage recursive transversal filter shown in Figure 5.7(b) with the feedback coefficients  $B_1$  and  $B_2$  determined from the plot in Figure 5.6(b). The maximum gain through this filter configuration is given by the equation for  $G_{MAX}$  (Figure 5.7(b)). Input signal values must be normalized by a gain =  $1/G_{MAX}$  or there will be overflows in the filter calculations.